Product Summary

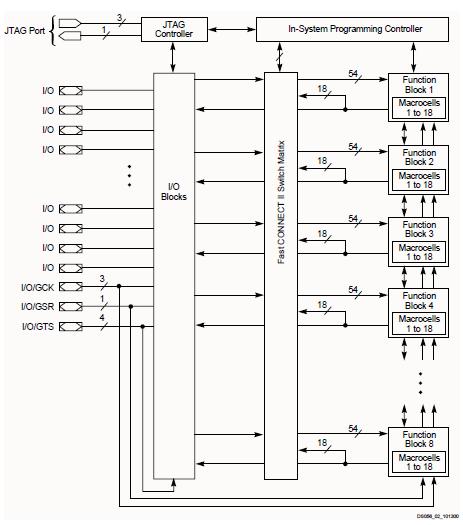

The XC95144XLTQG100AWN is a 3.3V CPLD targeted for high-performance, low-voltage applications in leading-edge communications and computing systems. The XC95144XLTQG100AWN is comprised of eight 54V18 Function Blocks, providing 3,200 usable gates with propagation delays of 5 ns.

Parametrics

XC95144XLTQG100AWN absolute maximum ratings: (1)Supply voltage relative to GND: -0.5 to 4.0 V; (2)Input voltage relative to GND: -0.5 to 5.5 V; (3)Voltage applied to 3-state output: -0.5 to 5.5 V; (4)Storage temperature (ambient): -65 to +150℃; (5)Maximum soldering temperature (10s @ 1/16 in. = 1.5 mm): +220℃; (6)Junction temperature: +150℃.

Features

XC95144XLTQG100AWN features: (1)5 ns pin-to-pin logic delays; (2)System frequency up to 178 MHz; (3)144 macrocells with 3,200 usable gates; (4)Available in small footprint packages: 100-pin TQFP (81 user I/O pins), 144-pin TQFP (117 user I/O pins), 144-CSP (117 user I/O pins); (5)Optimized for high-performance 3.3V systems: Low power operation, 5V tolerant I/O pins accept 5V, 3.3V, and 2.5V; (6)signals, 3.3V or 2.5V output capability, Advanced 0.35 micron feature size CMOS Fast FLASH technology.

Diagrams

|

XC9500 |

Other |

|

Data Sheet |

Negotiable |

|

||||||||||||||||

|

XC9500XV |

Other |

|

Data Sheet |

Negotiable |

|

||||||||||||||||

|

XC9501 |

Other |

|

Data Sheet |

Negotiable |

|

||||||||||||||||

|

XC9502 |

Other |

|

Data Sheet |

Negotiable |

|

||||||||||||||||

|

XC9503 |

Other |

|

Data Sheet |

Negotiable |

|

||||||||||||||||

|

XC9503B093AR-G |

|

IC REG BUCK ADJ 1A DL 10MSOP |

Data Sheet |

|

|

||||||||||||||||

(China (Mainland))

(China (Mainland))